THIRD EDITION

# VHDL

## Modular Design and Synthesis of Cores and Systems

ZAINALABEDIN NAVABI, PH.D.

## VHDL: Modular Design and Synthesis of Cores and Systems

### About the Author

Dr. Zainalabedin Navabi is a professor of electrical and computer engineering at Northeastern University. Dr. Navabi is the author of several textbooks and computer-based trainings on VHDL, Verilog, and related tools and environments. Dr. Navabi's involvement with hardware description languages began in 1976 when he started the development of a register-transfer level simulator for one of the very first Hardware Description Languages (HDLs). In 1981 he completed the development of a synthesis tool that generated MOS layout from an RTL description. Since 1981, Dr. Navabi has been involved in the design, definition, and implementation of HDLs. He has written numerous papers on the application of HDLs in simulation, synthesis, and test of digital systems. He started one of the first full HDL courses at Northeastern University in 1990. Since then he has conducted many short courses and tutorials on this subject in the United States and abroad. In addition to being a professor, he is also a consultant to Electronic Design Automation (EDA) companies. Dr. Navabi received his M.S. and Ph.D. from the University of Arizona in 1978 and 1981, and his B.S. from the University of Texas at Austin in 1975. He is a senior member of IEEE, and a member of IEEE Computer Society, ASEE, and ACM. Dr. Navabi is the author of eight books on various aspects of digital system design automation.

## VHDL: Modular Design and Synthesis of Cores and Systems

## Zainalabedin Navabi, Ph.D.

Professor of Electrical and Computer Engineering Northeastern University Boston, Massachusetts

Third Edition

New York Chicago San Francisco Lisbon London Madrid Mexico City Milan New Delhi San Juan Seoul Singapore Sydney Toronto Copyright © 2007 by The McGraw-Hill Companies. All rights reserved. Manufactured in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of the publisher.

0-07-150892-9

The material in this eBook also appears in the print version of this title: 0-07-147545-1.

All trademarks are trademarks of their respective owners. Rather than put a trademark symbol after every occurrence of a trademarked name, we use names in an editorial fashion only, and to the benefit of the trademark owner, with no intention of infringement of the trademark. Where such designations appear in this book, they have been printed with initial caps.

McGraw-Hill eBooks are available at special quantity discounts to use as premiums and sales promotions, or for use in corporate training programs. For more information, please contact George Hoare, Special Sales, at george\_hoare@mcgraw-hill.com or (212) 904-4069.

#### TERMS OF USE

This is a copyrighted work and The McGraw-Hill Companies, Inc. ("McGraw-Hill") and its licensors reserve all rights in and to the work. Use of this work is subject to these terms. Except as permitted under the Copyright Act of 1976 and the right to store and retrieve one copy of the work, you may not decompile, disassemble, reverse engineer, reproduce, modify, create derivative works based upon, transmit, distribute, disseminate, sell, publish or sublicense the work or any part of it without McGraw-Hill's prior consent. You may use the work for your own noncommercial and personal use; any other use of the work is strictly prohibited. Your right to use the work may be terminated if you fail to comply with these terms.

THE WORK IS PROVIDED "AS IS." McGRAW-HILL AND ITS LICENSORS MAKE NO GUARANTEES OR WARRANTIES AS TO THE ACCURACY, ADEQUACY OR COMPLETE-NESS OF OR RESULTS TO BE OBTAINED FROM USING THE WORK, INCLUDING ANY INFORMATION THAT CAN BE ACCESSED THROUGH THE WORK VIA HYPERLINK OR OTHERWISE, AND EXPRESSLY DISCLAIM ANY WARRANTY, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. McGraw-Hill and its licensors do not warrant or guarantee that the functions contained in the work will meet your requirements or that its operation will be uninterrupted or error free. Neither McGraw-Hill nor its licensors shall be liable to you or anyone else for any inaccuracy, error or omission, regardless of cause, in the work or for any damages resulting therefrom. McGraw-Hill has no responsibility for the content of any information accessed through the work. Under no circumstances shall McGraw-Hill and/or its licensors be liable for any indirect, incidental, special, punitive, consequential or similar damages that result from the use of or inability to use the work, even if any of them has been advised of the possibility of such damages. This limitation of liability shall apply to any claim or cause whatsoever whether such claim or cause arises in contract, tort or otherwise.

DOI: 10.1036/0071475451

## Want to learn more?

We hope you enjoy this McGraw-Hill eBook! If

you'd like more information about this book, its author, or related books and websites, please click here.

In the memory of my father, Mohammad-Hossein Navabi.

This page intentionally left blank

## CONTENTS

Preface xv Introduction xvii Acknowledgments xix

#### **CHAPTERS**

| 1 | Digit   | tal System Design Automation with VHDL | 1  |

|---|---------|----------------------------------------|----|

|   | 1.1     | Abstraction Levels                     | 2  |

|   | 1.2     | System Level Design Flow               |    |

|   | 1.2.1   | Hardware/Software Partitioning         |    |

|   | 1.2.2   | Hardware Part                          |    |

|   | 1.2.3   | Software Part                          |    |

|   | 1.3     | RTL Design Flow                        |    |

|   | 1.3.1   | Design Entry                           |    |

|   | 1.3.2   | Testbench in VHDL                      | 7  |

|   | 1.3.3   | Design Validation                      |    |

|   | 1.3.4   | Compilation and Synthesis              |    |

|   | 1.3.5   | Timing Analysis                        | 13 |

|   | 1.3.6   | Post-Synthesis Simulation              |    |

|   | 1.3.7   | Hardware Generation                    |    |

|   | 1.4     | VHDL                                   | 14 |

|   | 1.4.1   | VHDL Initiation                        |    |

|   | 1.4.2   | Existing Languages                     | 15 |

|   | 1.4.3   | VHDL Requirements                      |    |

|   | 1.4.4   | The VHDL Language                      |    |

|   | 1.5     | Summary                                | 21 |

|   | Problem | ns                                     | 21 |

|   | Suggest | ted Reading                            |    |

| 2 | RTL    | Design with VHDL                            | 23 |

|---|--------|---------------------------------------------|----|

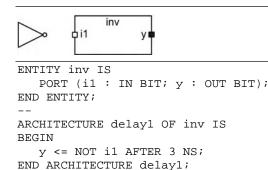

|   | 2.1    | Basic Structures of VHDL                    | 24 |

|   | 2.1.1  | Entities and Architectures                  | 25 |

|   | 2.1.2  | Entity-Architecture Outline                 | 27 |

|   | 2.1.3  | Entity Ports                                | 28 |

|   | 2.1.4  | Signals and Variables                       | 29 |

|   | 2.1.5  | Logic Value System                          | 31 |

|   | 2.1.6  | Resolutions                                 |    |

|   | 2.2    | Combinational Circuits                      |    |

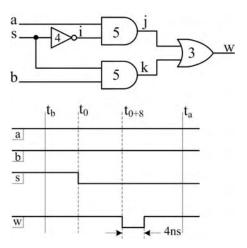

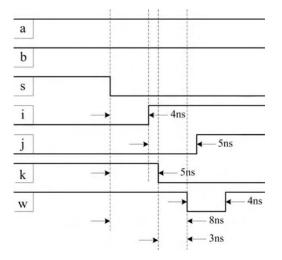

|   | 2.2.1  | Gate Level Combinational Circuits           |    |

|   | 2.2.2  | Gate Level Synthesis                        |    |

|   | 2.2.3  | Descriptions by Use of Equations            | 38 |

|   | 2.2.4  | Instantiating Other Modules                 |    |

|   | 2.2.5  | Synthesis of Assignment Statements          |    |

|   | 2.2.6  | Descriptions with Sequential Flow           |    |

|   | 2.2.7  | Combinational Rules                         | 49 |

|   | 2.2.8  | Bussing                                     | 49 |

|   | 2.2.9  | Synthesizing Procedural Blocks              | 50 |

|   | 2.3    | Sequential Circuits                         |    |

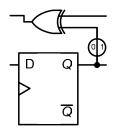

|   | 2.3.1  | Basic Memory Elements at the Gate Level     | 52 |

|   | 2.3.2  | Memory Elements Using Procedural Statements | 54 |

|   | 2.3.3  | Flip-flop Synthesis                         | 57 |

|   | 2.3.4  | Registers, Shifters and Counters            | 59 |

|   | 2.3.5  | Synthesis of Shifters and Counters          | 61 |

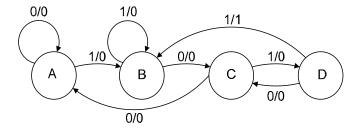

|   | 2.3.6  | State Machine Coding                        | 62 |

|   | 2.3.7  | State Machine Synthesis                     | 64 |

|   | 2.3.8  | Memories                                    | 65 |

|   | 2.4    | Writing Testbenches                         | 65 |

|   | 2.5    | Synthesis Issues                            | 68 |

|   | 2.6    | VHDL Essential Terminologies                | 68 |

|   | 2.6.1  | Design                                      | 68 |

|   | 2.6.2  | Analysis                                    | 68 |

|   | 2.6.3  | Library                                     | 69 |

|   | 2.6.4  | Standard Packages                           | 69 |

|   | 2.6.5  | Elaboration                                 | 70 |

|   | 2.6.6  | Event Driven Simulation                     | 70 |

|   | 2.6.7  | Concurrency                                 | 70 |

|   | 2.6.8  | Concurrent Bodies                           | 70 |

|   | 2.6.9  | Sequentiality                               | 70 |

|   | 2.6.10 | 1                                           |    |

|   | 2.6.11 | · · · · · · · · · · · · · · · · · · ·       |    |

|   | 2.6.12 | 2 Real Time                                 | 72 |

|   | 2.6.13 | 3 Delta Delay                               | 72 |

|   | 2.6.1  | 4 Scheduling                                | 73 |

|   | 2.6.18 | 5 Resolution                                | 73 |

|   | 2.6.16  | 3 Code Formal                                          | 73  |

|---|---------|--------------------------------------------------------|-----|

|   | 2.7     | Summary                                                | 73  |

|   | Problem | ns                                                     | 73  |

|   | Suggest | ed Reading                                             | 76  |

| 3 | VHD     | L Constructs for Structure and Hierarchy Descriptions. | 77  |

|   | 3.1     | Basic Components                                       |     |

|   | 3.1.1   | Basic Model                                            | 78  |

|   | 3.2     | Component Instantiations                               | 80  |

|   | 3.2.1   | Direct Instantiation                                   | 81  |

|   | 3.2.2   | Component Instantiation                                | 81  |

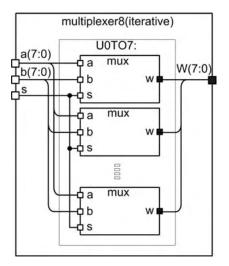

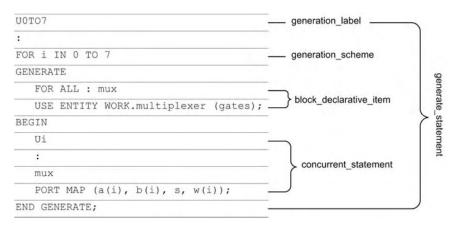

|   | 3.3     | Iterative Networks                                     | 84  |

|   | 3.3.1   | Multi-bit Vectors                                      | 85  |

|   | 3.3.2   | Multi-instance Generations                             | 85  |

|   | 3.3.3   | Simplified Generations                                 | 87  |

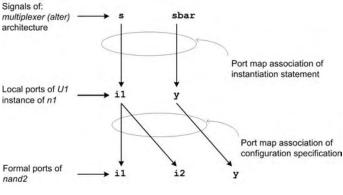

|   | 3.4     | Binding Alternatives                                   | 87  |

|   | 3.5     | Association Methods                                    | 89  |

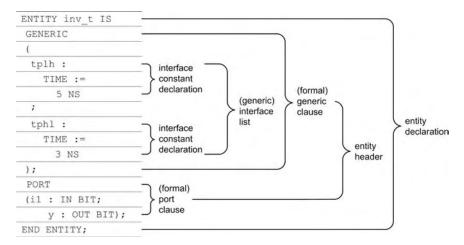

|   | 3.6     | Generic Parameters                                     |     |

|   | 3.6.1   | Using Generic Default Values                           | 91  |

|   | 3.6.2   | Generic Map Aspect                                     | 92  |

|   | 3.6.3   | Generic Association List                               |     |

|   | 3.7     | Design Configuration                                   | 94  |

|   | 3.7.1   | Basic Configuration Declaration                        |     |

|   | 3.7.2   | Incremental Configuration                              | 96  |

|   | 3.7.3   | Configuring Nested Components                          | 97  |

|   | 3.7.4   | Indexing Block Configurations                          |     |

|   | 3.7.5   | Instantiating a Design Unit                            |     |

|   | 3.8     | Design Simulation                                      | 101 |

|   | 3.9     | Summary                                                |     |

|   | Problem | ns                                                     | 103 |

|   | Suggest | ed Reading                                             | 104 |

| 4 | Con     | current Constructs for RT Level Descriptions           | 105 |

|   | 4.1     | Concurrent Signal Assignments                          |     |

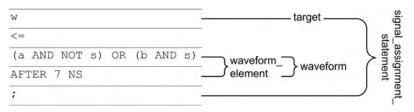

|   | 4.1.1   | 1 8                                                    | 106 |

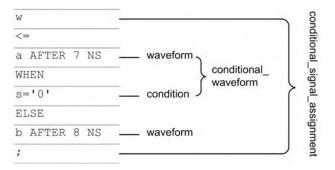

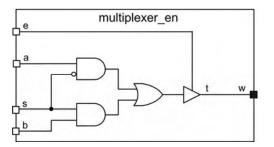

|   | 4.1.2   | Conditional Signal Assignment                          | 107 |

|   | 4.1.3   | 0 0                                                    |     |

|   | 4.2     | Guarded Signal Assignments                             | 111 |

|   | 4.2.1   | GUARD Signal and Expression                            |     |

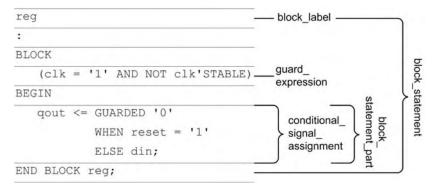

|   | 4.2.2   | Block Statement                                        |     |

|   | 4.2.3   | Block Statement Ports                                  |     |

|   | 4.2.4   | Nested Block Statements                                | 114 |

|   | 4.2.5   | Guarded Signals                                        |     |

|   | 4.2.6   | Timing Disconnections                                  | 118 |

|   | 4.3     | Summary                                                | 120 |

|   | Problem         | ns                                           |     |

|---|-----------------|----------------------------------------------|-----|

|   | Suggest         | ted Reading                                  |     |

|   |                 |                                              |     |

| 5 | -               | uential Constructs for RT Level Descriptions |     |

|   | 5.1             | Process Statement                            |     |

|   | 5.1.1           | Declarative Part of a Process                |     |

|   | 5.1.2           | Statement Part of a Process                  |     |

|   | 5.1.3           | Process Sensitivity List                     |     |

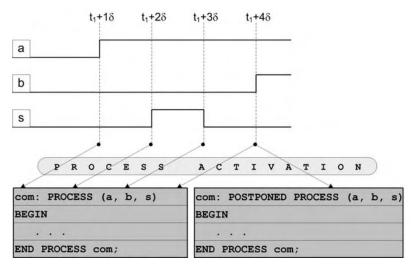

|   | 5.1.4           | Postponed Processes                          |     |

|   | 5.1.5           | Passive Processes                            |     |

|   | 5.2             | Sequential Wait Statements                   |     |

|   | 5.3             | VHDL Subprograms                             |     |

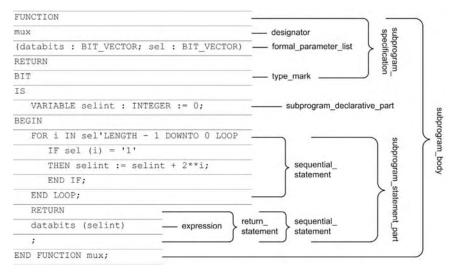

|   | 5.3.1           | Function Definition                          |     |

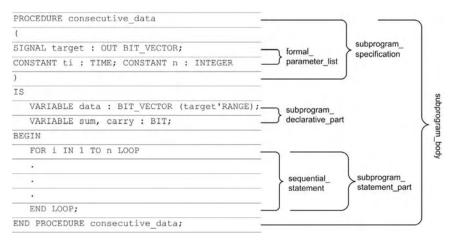

|   | 5.3.2           | Procedure Definition                         |     |

|   | 5.3.3           | Language Aspects of Subprograms              |     |

|   | 5.3.4           | Nesting Subprograms                          |     |

|   | 5.4             | VHDL Library Structure                       |     |

|   | 5.4.1           | Creating Libraries                           |     |

|   | 5.4.2           | Using Libraries                              |     |

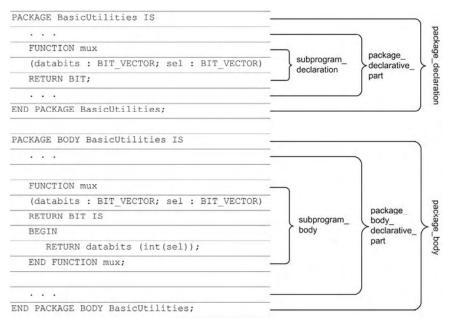

|   | 5.5             | Packaging Utilities and Components           |     |

|   | 5.5.1           | A Package of Utilities                       |     |

|   | 5.5.2           | A Package of Components                      |     |

|   | 5.6             | Sequential Statements                        |     |

|   | 5.6.1           | If Statement                                 |     |

|   | 5.6.2           | Loop Statement                               |     |

|   | 5.6.3           | Case Statement                               |     |

|   | 5.6.4           | Assertion Statement                          |     |

|   | 5.7<br>Daalalaa | Summary                                      |     |

|   |                 | ns                                           |     |

|   | Suggest         | ted Reading                                  | 160 |

| 6 | ИНО             | L Language Utilities and Packages            | 161 |

| Č | 6.1             | Type Declarations and Usage                  |     |

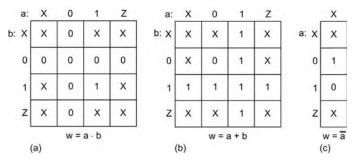

|   | 6.1.1           | Enumeration Type for Multi-Value Logic       |     |

|   | 6.1.2           | Using Real Numbers                           |     |

|   | 6.1.3           | Type Conversions                             |     |

|   | 6.1.4           | Physical Types                               |     |

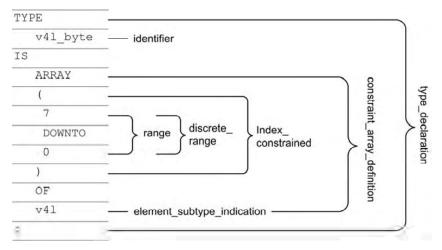

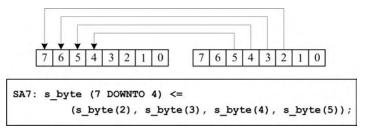

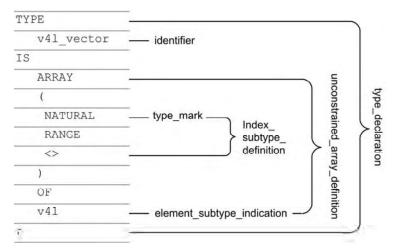

|   | 6.1.5           | Array Declarations                           |     |

|   | 6.1.6           | File Type and External File I/O              |     |

|   | 6.2             | VHDL Operators                               |     |

|   | 6.2.1           | Logical Operators                            |     |

|   | 6.2.2           | Relational Operators                         |     |

|   | 6.2.3           | Shift Operators                              |     |

|   | 6.2.4           | Adding Operators                             |     |

|   | 6.2.5           | Sign Operators                               |     |

|   | JJ              | ~-8 • Potetote                               |     |

|   | 6.2.6   | Multiplying Operators                     | 189 |

|---|---------|-------------------------------------------|-----|

|   | 6.2.7   | Other Operators                           |     |

|   | 6.2.8   | Aggregate Operation                       |     |

|   | 6.3     | Operator and Subprogram Overloading       |     |

|   | 6.3.1   | Operator Overloading                      |     |

|   | 6.3.2   | Subprogram Overloading                    | 193 |

|   | 6.4     | Other Types and Type-Related Issues       |     |

|   | 6.4.1   | Subtypes                                  | 194 |

|   | 6.4.2   | Record Types                              | 195 |

|   | 6.4.3   | Alias Declaration                         | 197 |

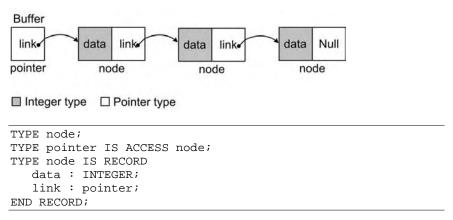

|   | 6.4.4   | Access Types                              |     |

|   | 6.4.5   | Global Objects                            | 202 |

|   | 6.4.6   | Type Conversions                          | 203 |

|   | 6.4.7   | Standard Nine-Value Logic                 | 204 |

|   | 6.5     | Predefined Attributes                     |     |

|   | 6.5.1   | Array Attributes                          |     |

|   | 6.5.2   | Type Attributes                           |     |

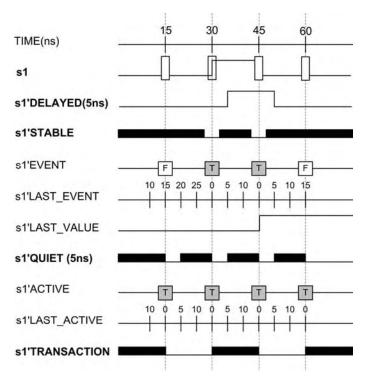

|   | 6.5.3   | Signal Attributes                         |     |

|   | 6.5.4   | Entity Attributes                         | 213 |

|   | 6.5.5   | User-Defined Attributes                   |     |

|   | 6.6     | Standard Libraries and Packages           |     |

|   | 6.6.1   | STANDARD Package                          |     |

|   | 6.6.2   | TEXTIO Package and ASCII I/O              |     |

|   | 6.6.3   | - 0 - 0                                   |     |

|   | 6.6.4   | Std_logic_arith Package                   |     |

|   | 6.7     | Summary                                   |     |

|   |         | ns                                        |     |

|   | Suggest | ted Reading                               |     |

| 7 | VHD     | L Signal Model                            | 227 |

|   | 7.1     | Characterizing Hardware Languages         |     |

|   | 7.1.1   | Timing and Concurrency of Operations      |     |

|   | 7.2     | Signal Assignments                        | 230 |

|   | 7.2.1   | Inertial Delay Mechanism                  | 231 |

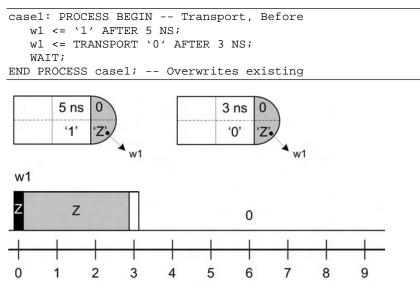

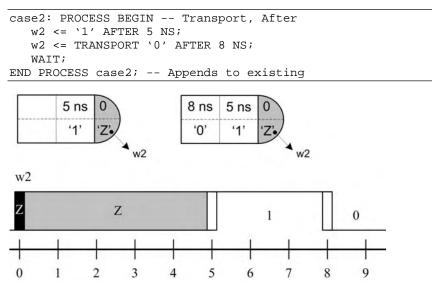

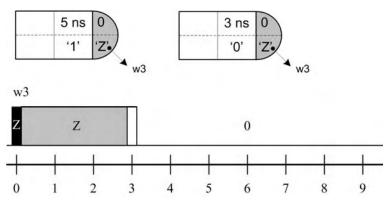

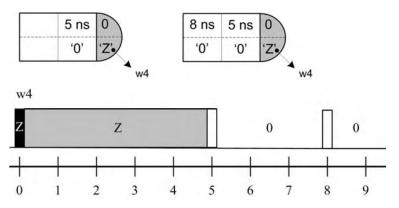

|   | 7.2.2   | Transport Delay Mechanism                 | 232 |

|   | 7.2.3   | Comparing Inertial and Transport          |     |

|   | 7.3     | Concurrent and Sequential Assignments     |     |

|   | 7.3.1   | Concurrent Assignments                    |     |

|   | 7.3.2   | Events and Transactions                   | 234 |

|   | 7.3.3   | Delta Delay                               |     |

|   | 7.3.4   | Sequential Placement of Transactions      |     |

|   | 7.4     | Multiple Concurrent Drivers               |     |

|   | 7.4.1   | Resolving between Multiple Driving Values |     |

|   | 7.4.2   | Resolutions with Guarded Assignments      |     |

|   | 7.4.3   | Resolving INOUT Signals                   |     |

|   | 7.4.4        | Standard Resolution                             | 268 |

|---|--------------|-------------------------------------------------|-----|

|   | 7.5          | Summary                                         | 268 |

|   |              | 18                                              |     |

|   | Suggest      | ed Reading                                      | 272 |

| ~ | Hand         | human Course and Madala                         | 070 |

| 8 |              | ware Cores and Models                           |     |

|   | 8.1<br>8.1.1 | Synthesis Rules and Styles                      |     |

|   | 0            |                                                 |     |

|   | 8.1.2        | Sequential Cores                                |     |

|   | 8.1.3        | Finite State Machines                           |     |

|   | 8.2          | Memory and Queue Structures                     |     |

|   | 8.2.1        | Generic RAM Core                                |     |

|   | 8.2.2        | Synthesizable Push-Pop Stack                    |     |

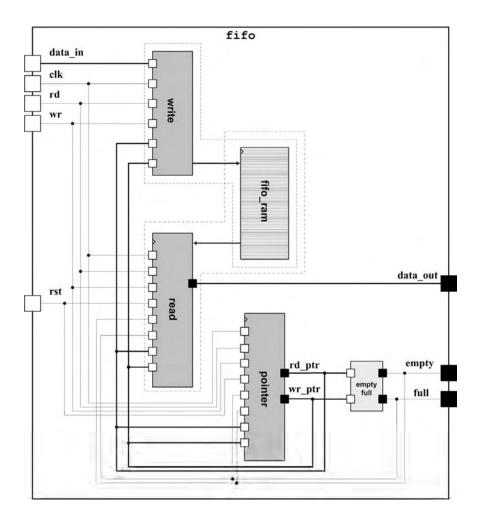

|   | 8.2.3        | Synthesizable Circular FIFO                     |     |

|   | 8.2.4        | Dynamic Access Type FIFO                        |     |

|   | 8.3          | Arithmetic Cores                                |     |

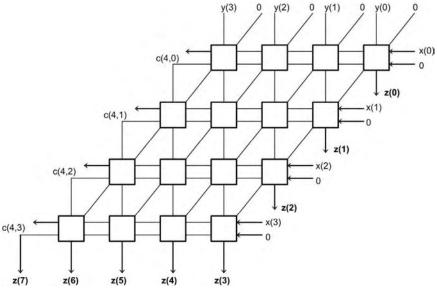

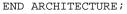

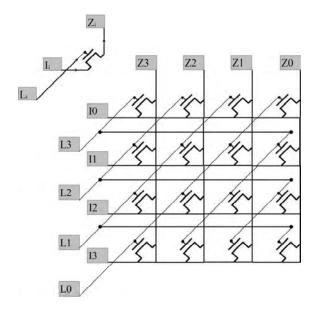

|   | 8.3.1        | Array Multiplier                                |     |

|   | 8.3.2        | Carry-Lookahead Adder                           |     |

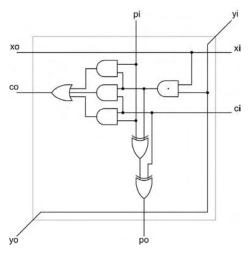

|   | 8.3.3        | Synthesizable Booth Multiplier                  |     |

|   | 8.4          | Components with Separate Control and Data Parts |     |

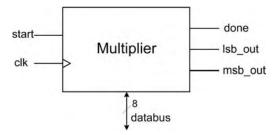

|   | 8.4.1        | Sequential Multiplier                           |     |

|   | 8.4.2        | von Neumann Computer Model                      |     |

|   | 8.5          | Summary                                         |     |

|   |              | 18                                              |     |

|   | Suggest      | ed Reading                                      | 340 |

| 9 | Core         | Design Test and Testability                     | 341 |

| - | 9.1          | Issues Related to Design Test                   |     |

|   | 9.1.1        | -                                               |     |

|   | 9.1.2        | Testbench                                       |     |

|   | 9.1.3        | Coverage                                        |     |

|   | 9.2          | Simple Testbenches                              |     |

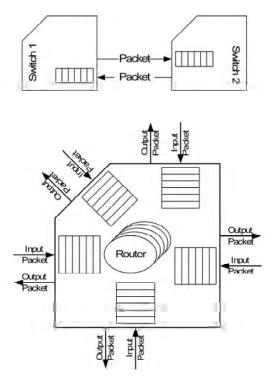

|   | 9.2.1        | Combinational Circuit Testing                   |     |

|   | 9.2.2        | Sequential Circuit Testing                      |     |

|   | 9.3          | Testbench Techniques                            |     |

|   | 9.3.1        | Arbitrary Test Data                             | 347 |

|   | 9.3.2        | Random Test Data                                | 348 |

|   | 9.3.3        | Applying Synchronized Data                      | 351 |

|   | 9.3.4        | Synchronized Display of Results                 |     |

|   | 9.3.5        | Displaying Interval Objects                     |     |

|   | 9.3.6        | An Interactive Testbench                        |     |

|   | 9.3.7        | Queued Data Application                         |     |

|   | 9.3.8        | Text File Stimuli and Response                  |     |

|   | 9.4          | Complete System Testing                         |     |

|   | 9.4.1        | Multiplier Testing                              |     |

|   |              |                                                 |     |

| 9.4.2    | Processor Testing                            |     |

|----------|----------------------------------------------|-----|

| 9.5      | Issues Related to Manufacturing Test         |     |

| 9.5.1    | Manufacturing Test                           | 371 |

| 9.5.2    | Fault Model                                  |     |

| 9.5.3    | Test Generation                              |     |

| 9.5.4    | Fault Simulation                             |     |

| 9.5.5    | Fault Coverage                               |     |

| 9.5.6    | Testability                                  |     |

| 9.6      | Core Test Support Modules                    |     |

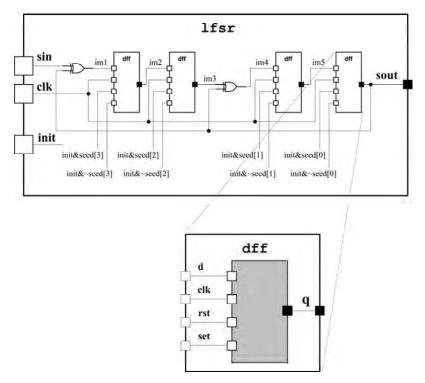

| 9.6.1    | LFSR                                         |     |

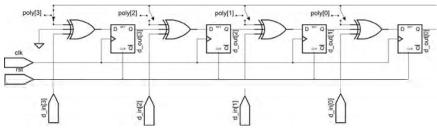

| 9.6.2    | MISR                                         |     |

| 9.7      | Scan Design and Test Application             |     |

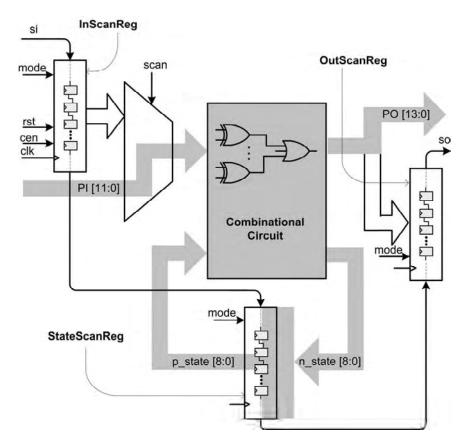

| 9.7.1    | Starting Design                              | 377 |

| 9.7.2    | Scan Insertion                               |     |

| 9.7.3    | Scan Testbench                               |     |

| 9.7.4    | Top Level Tester                             |     |

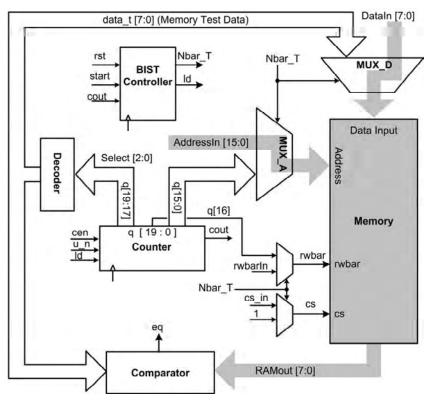

| 9.8      | Memory BIST                                  |     |

| 9.8.1    | Memory BIST Architecture                     |     |

| 9.8.2    | Test Session                                 |     |

| 9.8.3    | BIST Controller                              |     |

| 9.8.4    | BIST Structure                               |     |

| 9.8.5    | BIST Tester                                  |     |

| 9.9      | Summary                                      |     |

| Problem  | s                                            |     |

| Suggeste | ed Reading                                   |     |

|          |                                              |     |

|          | In, Test and Application of a Processor Core |     |

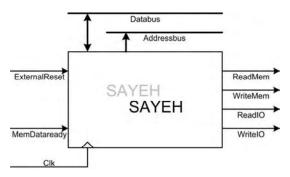

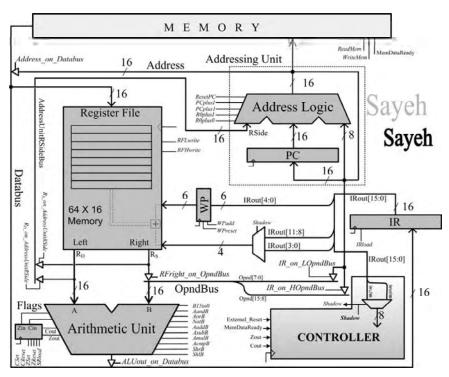

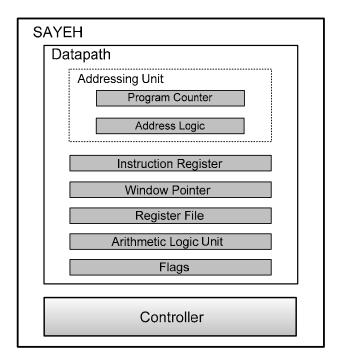

|          | Design of SAYEH Processor Core               |     |

| 10.1.1   | 5                                            |     |

| 10.1.2   | 1                                            |     |

|          | SAYEH VHDL Description                       |     |

| 10.2.1   | Data Components                              |     |

| 10.2.2   | 1                                            |     |

| 10.2.3   |                                              |     |

| 10.2.4   | Complete SAYEH Processor                     |     |

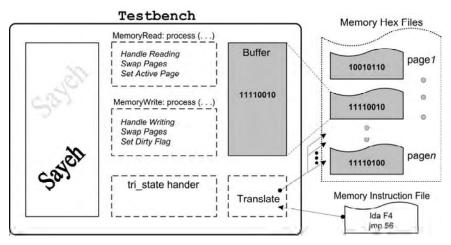

|          | SAYEH Testbench / Assembler / Memory Model   |     |

| 10.3.1   | Top Level VHDL Testbench                     |     |

|          | Memory Model                                 |     |

| 10.3.3   | Assembler                                    |     |

| 10.3.4   | Memory Read                                  |     |

| 10.3.5   | Memory Write                                 |     |

| 10.3.6   | Memory File Handling                         |     |

| 10.3.7   | Sorting Test Program                         |     |

|          | SAYEH as an Embedded Processor Core          |     |

| 10.4.1   | Embedded Core Based Design                   |     |

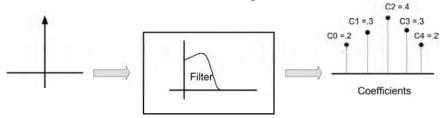

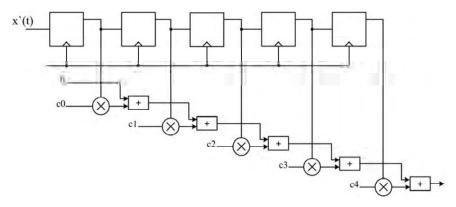

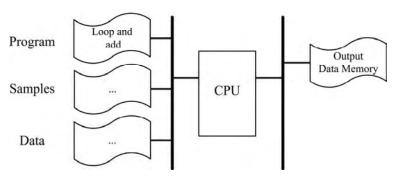

| 10.4.2    | Filter Design           |  |

|-----------|-------------------------|--|

|           | Core Based Architecture |  |

| 10.4.4    | FIR Program             |  |

| 10.4.5    | FIR Memory and IO Maps  |  |

| 10.4.6    | Filter Software         |  |

| 10.5 Sı   | ammary                  |  |

| Problems. | -                       |  |

| Suggested | Reading                 |  |

|           |                         |  |

#### APPENDIXES

| Α    | VHDL Keywords4                                            | 39  |

|------|-----------------------------------------------------------|-----|

| В    | VHDL Language Grammar4                                    | 41  |

| С.   | VHDL Standard Packages41STANDARD Package42TEXTIO Package4 | 61  |

| D    | STD_LOGIC_1164 Package4                                   | 67  |

| Е    | STD_LOGIC_TEXTIO Package4                                 | 79  |

| F    | STD_LOGIC_ARITH Package4                                  | 81  |

| G    | STD_LOGIC_SIGNED4                                         | 97  |

| н    | STD_LOGIC_UNSIGNED5                                       | 03  |

| I    | math_real Package5                                        | 09  |

| Inde | ×5                                                        | 523 |

## PREFACE

This book is on the IEEE Standard 1076 VHDL hardware description language and the utilization of this language for the design of modern digital systems. The intended audiences are engineers involved in various aspects of digital systems design and manufacturing and students with the basic knowledge of digital system design. The emphasis of the book is on using VHDL for the design, test, and synthesis of digital systems. We will discuss Register Transfer (RT) level digital system design, and discuss how VHDL can be used in this design flow. The book covers development, test, and utilization of configurable cores for RT level design. In addition, we discuss design and utilization of a processor core for embedded system designs.

In the last few years RT level design of digital systems has gone through significant changes. Beyond simulation and synthesis that are now parts of any RTL design process, we are looking at testbench generation and design validation tools and schemes. As with any book on VHDL, this book covers digital design and VHDL for simulation and synthesis. However, to ready design engineers for designing, testing, and verifying large digital system designs, the book contains material for testbench development and testable design.

Design strategy, digital design tools, and the role of VHDL in a modern digital design environment are discussed in Chapter 1 of this book. In the design strategy part we discuss where and how RT level cores are used, what parts of a design are handled by a program running on a processor core, and what parts of a large design are coded in an HDL like VHDL. With this multi domain design methodology, the role of design tools and a common design representation that suits all these domains become very important. We will show that the VHDL language is a suitable language for representation of a design, the components of which are described at different domains. The introductory part of this book outlines the tools needed in a digital design environment and discusses how these tools benefit digital designers. We will show that at the present time the majority of designers do take advantage of simulation and synthesis tools. Because of this, the book focuses on VHDL simulation semantics and synthesizability of designs. Design error detection by simulation is only possible if the design is simulated with a proper testbench and good design coverage is obtained. For this reason, the book devotes a major chapter to the issue of testbench development. We will also discuss testable designs and develop testbenches for these designs as well.

One of the key subjects treated in this book is the linguistics of the VHDL, including its type oriented semantics, simulation model, and concurrency handling. We believe, to be able to utilize VHDL beyond just an RTL design front-end, and keep up with the changing technology, and to be able to find new ways of using this language for tomorrow's complex designs, a thorough understanding of the language semantics and linguistics aspects of VHDL is required. This belief is why we have devoted a major part of this book to the linguistics and simulation model of VHDL.

This book covers basic VHDL for simulation and synthesis, details of language simulation semantics and syntax, configurable core design, core testing, and processor cores and their applications. These topics are kept separate to allow a designer interested in basic simulation and synthesis to use the book for just that. On the other hand, those who are interested in the linguistics of VHDL can use the parts of the book that are intended for this purpose and use the book as a complete reference. Furthermore advanced designers and test engineers have their own chapters to gather their required information.

In an academic setting, in an undergraduate course the book can be used as a design book with less emphasis on the linguistics and language semantics, and for a graduate course the complete book provides enough material for one semester.

> Zainalabedin Navabi navabi@ece.neu.edu Boston, Massachusetts March, 2007

## INTRODUCTION

Over the years, design of digital systems has evolved from transistor level logic to RTL. In today's technology, RT level design has reached its level of maturity and new, more abstract design methods are being searched for. With the present level of maturity of RTL and RT level tools, we should go one step beyond just simulation and synthesis and look into new ways a hardware description language like VHDL can help designers.

Toward this goal, and in order to prepare designers for future design challenges, we have concentrated on two key issues. One is that the linguistics and semantics of the VHDL are thoroughly covered. The second contribution of this book is its coverage of testbenches and testability techniques.

In addition to looking at the future of RTL, this book gets deep into today's RT level design by presenting synthesis techniques and developing configurable cores for a core-based design environment. The design of a general purpose processor core in the last chapter of this book is another way to enhance RT level designs by using embedded processors.

VHDL: Modular Design and Synthesis of Cores and Systems covers RTL, system level design methodology, VHDL language syntax and semantics, HDL simulation model, design of configurable cores, testbench and testable design description in VHDL, and processor cores. This book can be used in an academic or industrial setting by students or engineers. In either case it assumes a general knowledge of logic design. The early part of this book provides enough information for simulation and synthesis of basic RT level components. This information is useful for continuing to design and practice the language while more advanced topics are learned in the later chapters of the book. The first two chapters cover design strategy and simulation and synthesis of basic components. With these two chapters, readers will be able to start writing VHDL codes and perform simulation and synthesis of basic components.

The next three chapters discuss VHDL language syntax and semantics at the structural, functional, and behavioral levels, respectively. The chapters that follow discuss VHDL types and simulation model. These five chapters cover VHDL from a linguistic point of view.

After the discussion of the language, a chapter discusses configurable core design and another chapter talks about core testing and testbench development. The final chapter shows design, test and utilization of a processor core. Advanced modern designers will greatly benefit from the last three chapters of the book.

Chapter 1 discusses the general flow of a system level design and the role of compilers and synthesis tools. We discuss where VHDL fits in a modern digital design environment. A brief history of VHDL is given in this chapter.

Chapter 2 presents VHDL for those who want to get immediately started with design with VHDL. A section in this chapter covers VHDL definitions and terminologies.

Chapters 3 to 5 cover VHDL structural, concurrent, and behavioral constructs for describing RT level components.

Chapter 6 focuses on the linguistics issues of VHDL. Issues such as type definitions and overloading are covered here.

Chapter 7 discusses the signal and simulation model of VHDL. Multiple concurrent assignments to signals and scheduling values for signals are discussed here.

Chapter 8 presents VHDL descriptions for several configurable RT level cores. Several arithmetic, memory, queue, and processor cores are presented here.

Chapter 9 shows test techniques for RT level cores. It presents several testbench generation techniques and several testable designs coded in VHDL.

Chapter 10 is the last chapter of this book. This chapter shows the RT level design of a processor core. The processor core is then tested using methods discussed in Chapter 9. The last part of this chapter shows design of a filter using this processor core.

## ACKNOWLEDGMENTS

Several people helped me with preparation of this manuscript. My students Ms. Elnaz Koopahi and Ms. Mahshid Sedghi wrote models for many of the examples of Chapters 8 and 9. In addition they helped with the review of the book and made many useful comments for improving the book. Ms. Sedghi was very helpful in reviewing Chapter 10, debugging the processor model and developing a testbench for it.

Students in my VHDL class helped review the material and provided feedback on the flow of the material.

As with all my other publishing works, Ms. Fatemeh Asgari helped me with the preparation of the manuscript. She worked with me on the initial planning of this work, distribution of tasks during the project, and final assembly of this book. Her planning and organization has always been a key to successful completion of such projects.

I also thank my wife, Irma Navabi, for help, encouragement, and understanding my working habits. Such an intensive work could not be done without the support of my wife and two sons, Arash and Arvand. I thank them for this and my other scientific achievements. This page intentionally left blank

## Digital System Design Automation with VHDL

The early schematic capture and design entry programs used for design of digital systems have given way to complex design entry programs utilizing software programs, hardware cores, and components described in hardware description languages. Today's hardware designers designing complex hardware/software systems must be familiar with software programming, hardware description languages, and utilization of embedded cores for implementation of hardware and software parts of a system. In addition, hardware designers must be familiar with design environments utilizing software programs, HDL hardware descriptions, and embedded processor and intellectual property (IP) cores.

This chapter gives an overview of the hardware design process and the role of VHDL in a modern digital design methodology. We begin by an overview of levels of abstraction from systems to transistors. This discussion becomes useful in presenting design strategies that are based on recursive partitioning of a design into lower abstraction levels. Following this, we talk about hardware/software codesign, and discuss partitioning a design into a part that is to be implemented using various hardware design abstractions, and a part that is to be implemented with a software program. The section that comes after this discussion of partitioning focuses on RT level design that is the major abstraction level that the VHDL language is used for. We will talk about RT level simulation, synthesis and device programming tools, and will discuss the existing CAD tools used in this hardware design process. The last part of this chapter gives a general overview of the properties of the VHDL language.

#### 1.1 Abstraction Levels

Digital design started with putting transistors together to implement a given hardware function. Obviously this handcrafted method of design and flexibilities offered in choice of transistor size and routing of wires, achieves an optimum design for a given function.

On the other hand, as designs become more complex, this level of design had to change to allow design of large circuits. In an evolutionary process, gate level designs replaced transistor level designs. With this move to an upper abstraction level, compromise for timing, silicon utilization, and power consumptions had to be made. In addition, design tools were developed to help designers with utilization of gates verification of designs, and translation to the transistor level.

As designs became more complex, another higher abstraction level evolved that included even less detail than the gate level. The main focus of this level of abstraction is how transfer of data happens between registers, logic units, and busses; and because of this, it is referred to as register transfer level, or RTL. As in the move from transistor level to gate level, moving from gates to RT level carries with it compromises and tradeoffs. Furthermore, this higher level of abstraction requires use of tools and various software and hardware packages to aid the designer in the design process. As in the gate level, RT level tools include those for design capture, verification, and translation from RT level to the lower abstraction level, i.e., gate level synthesis.

For the same reasons that design had to go up from gate to RT level, the time of sole RT level design had to expire, and this level of abstraction had to give way to an upper level of abstraction, which for now, we refer to as Electronic System Level (ESL) or just system level. At the system level, a designer is only concerned with the functionality of the system being designed, and describes the algorithm that is going to be implemented. The algorithm is described using a procedural language like the C language. The description at this level does not contain clock or gate level timing.

System level tools include design entry tools, simulators, and, of course, hardware generation programs. Hardware generation from a system level description can be done in one of two possible ways. As in other abstraction levels, one way of generating hardware is to translate a system level description to a lower level of abstraction, i.e., RTL. Alternatively, a system level procedural description can be compiled to run on a given processor. This alternative is possible at the system level because the description is procedural and a software language like C can be used for it.

The above mentioned method of hardware generation (using a software program) from a system level description is what has be-

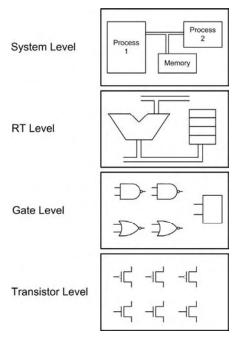

come embedded system design. The former method, i.e., translation from system to RTL, is often referred to as C synthesis, or system level synthesis. C synthesis refers to generation of hardware from a C program, or a procedural description. Figure 1.1 shows abstraction levels discussed here.

Figure 1.1 Abstraction Levels

#### 1.2 System Level Design Flow

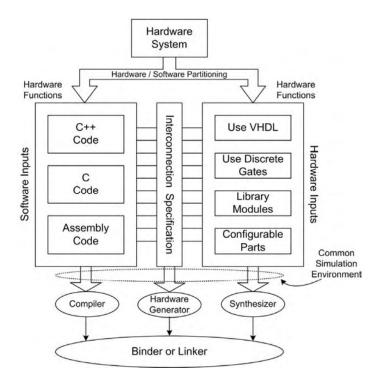

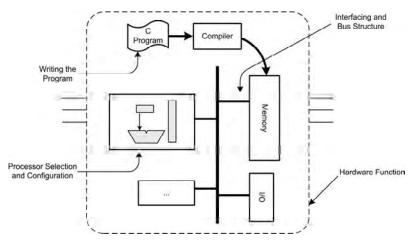

Figure 1.2 shows a design flow that consists of hardware and software parts. In this flow some hardware functions we implemented with RTL coding and same other functions are implemented by programs running on processor cores. The subsections below describe the details of this block diagram.

#### 1.2.1 Hardware/Software Partitioning

The first step in design at the system level is to decide what parts are to be implemented using predefined cores, RTL VHDL modules, or discrete components, and which parts are to be implemented with a program running on a processor core. This decision is referred to as hardware/software partitioning. This is a manual (or semi-manual) process, and is perhaps the most difficult system design phase.

Figure 1.2 Hardware/Software Design Flow

The hardware part becomes a description of various hardware modules that are described in an HDL or are available as predefined hardware modules. The software part is a high level C/C++ program that after being compiled becomes the memory contents of processor that runs the program.

#### 1.2.2 Hardware Part

The hardware part (right flow in Figure 1.2) of a complete hardware/software system may be composed of components that are described in VHDL, IP cores or discrete parts. Using tools and design environments, a hardware designer chooses to code parts of his or her design in VHDL, or use parts from a library of predefined modules.

Often a design environment provides intellectual property (IP) cores that designers can use and integrate in their designs. Hardware design environments also include configurable parts for commonly used components such as arithmetic functions, register banks, and counters.

#### 1.2.3 Software Part

The left flow in Figure 1.2 shows the implementation of the software part of a system. The part of a design that is to be implemented in software must become a machine language program in a given processor. The designer may choose to code this part in a high level language and compile it, or directly code it in assembly or machine language.

All the necessary software tools and compilers are available to a designer who uses a supported processor core. In this case, use of C/C++ for describing the software part of a system is the most logical choice, since compilation and debugging tools are provided for the designer. On the other hand, if a designer uses his or her own processor or a processor core that does not have a strong support, the designer is responsible for generating the machine language of the program he or she is implementing.

Regardless of how the programming task is done, after the completion of the design of the software part, this part looks like any hardware block with inputs and outputs. The inputs and outputs are either external to the system being designed, or they are to interconnect the hardware and software parts.

The sections that follow elaborate on the hardware and software sides of the design processes depicted in Figure 1.2.

#### 1.3 RTL Design Flow

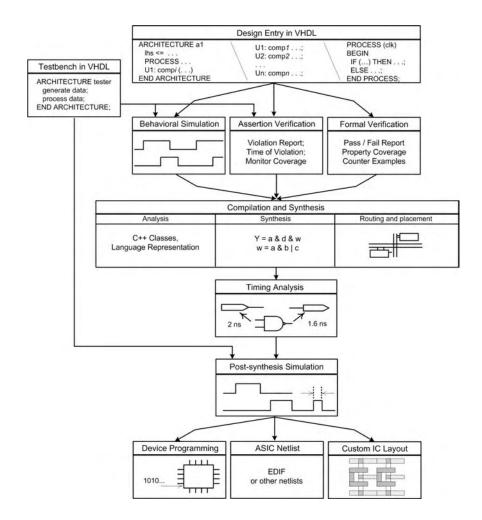

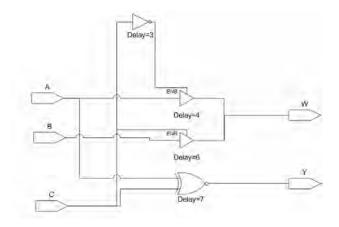

For the design of a digital system using an automated design environment, the design flow begins with specification of the design at various levels of abstraction and ends with generating netlist for an ASIC (application specific integrated circuits), layout for a custom IC, or a program for a PLD (programmable logic devices). Figure 1.3 shows steps involved in this design flow.

In the design entry phase, a design is specified as a mixture of behavioral VHDL code, instantiation of VHDL modules, and bus and wire assignments. A design engineer is also responsible for generating testbenches for his or her design for verification of the design and later for verifying the synthesis output. Design verification can be done by simulation, assertion verification, formal verification, or a mix of all three. After performing this design validation phase (this is called the pre-synthesis verification), this design is taken through the synthesis process to translate it into actual hardware of a target device. Here, target device refers to the specific field programmable logic device (FPLD) that is being programmed, the ASIC that is being manufactured by an outside source, or the custom IC that is being fabricated. After the synthesis process and before the actual hardware is generated, another simulation, that is referred to as postsynthesis simulation, is done. This simulation can take advantage of the same testbench generated for the VHDL model of the system before it is synthesized. This way, the behavioral model of the design and its hardware model are tested with the same data. The difference between pre- and post-synthesis simulations is in the level of details obtained from each simulation.

The sections that follow elaborate on each of the blocks shown in Figure 1.3. Most VHDL based EDA environments provide blocks shown in this figure.

#### 1.3.1 Design Entry

The first step in the design of a digital system is the design entry phase. In this phase, the design is described in VHDL in a top-down hierarchical fashion. A complete design may consist of components at the gate or transistor level, behavioral parts describing high level functionality of a hardware module, or components described by their bussing structure.

Because high-level VHDL designs are usually described at the level that specifies system registers and transfer of data between registers through busses, this level of system description is referred to as register transfer level. A complete design described as such has a clear hardware correspondence. VHDL constructs used in an RT level design are sequential statements, signal assignments, and instantiation statements.

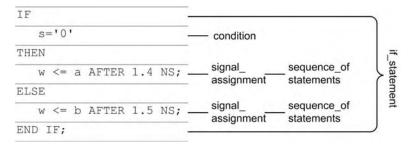

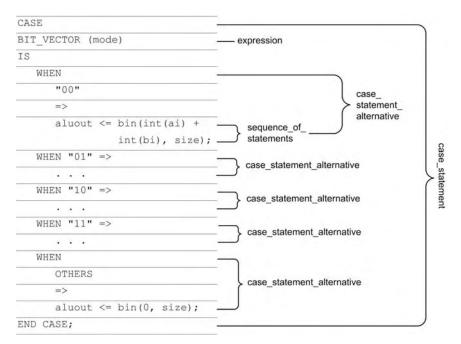

VHDL sequential statements are used for high level behavioral descriptions. A system or a component is described in a sequential fashion similar to the way processes are described in a software language. For example, we can describe a component by checking its input conditions, setting flags, waiting for events to occur, monitoring handshaking signals, and issuing outputs. Describing a system sequentially, VHDL if-then, case and other software-language-like constructs can be used.

VHDL *signal assignments* are statements for representing logic blocks, bus assignments and bus and input/output interconnect specifications. Combined with Boolean and conditional assignments, these language constructs can be used for describing components and systems in terms of their register and bus assignments.

VHDL *instantiation statements* are for using lower level components in an upper level design. Instead of describing behavior, functionality, or bussing of a system, we can describe a system in VHDL in terms of its lower level components. These sub-components can be as small as a gate or a transistor, or as large as a complete processor.

Figure 1.3 HDL Based Design Flow

#### 1.3.2 Testbench in VHDL

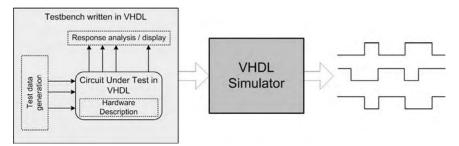

A system designed in VHDL must be simulated and tested for functionality before it is turned into hardware. In this simulation pass, design errors and incompatibility of components used in the design can be detected. Simulating a design requires generation of test data and observation of simulation results. This process can be done by use of a VHDL module that is referred to as a testbench. A VHDL testbench uses high-level constructs of this language for data generation, response monitoring, and even handshaking with the design. Inside the testbench, the design that is being simulated is instantiated. The testbench together with the design form a simulation model used by a VHDL simulation engine.

#### 1.3.3 Design Validation

An important task in any digital design is design validation. Design validation is the process that a designer checks his or her design for any design flaws that may have occurred in the design process. A design flaw can happen due to ambiguous problem specifications, designer errors, or incorrect use of parts in the design. Design validation can be done by simulation, assertion verification, or formal verification.

**1.3.3.1 Simulation.** Simulation for design validation is done before a design is synthesized. This simulation pass is also referred to as behavioral, RT-level, or pre-synthesis simulation. At the RT level a design includes clock level timing but no gate and wire delays are included. Simulation at this level is accurate to the clock level. Timing of RT level simulation is at the clock level and does not usually consider hazards, glitches, race conditions, setup and hold violations and other detailed timing issues. The advantage of this simulation is its speed compared with simulations at the gate or transistor levels.

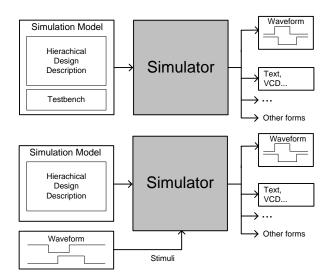

Figure 1.4 Using a Testbench or a Waveform Editor for Simulation

Simulation of a design requires test data, and usually VHDL simulation environments provide various methods for application of

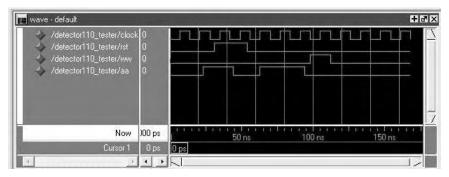

this data to the design being tested. Test data can be generated graphically using waveform editors, or through a testbench. Figure 1.4 shows two alternatives for defining test input data for a simulation engine. Outputs of simulators are in the form of waveforms (for visual inspection) and text for large designs for machine processing.

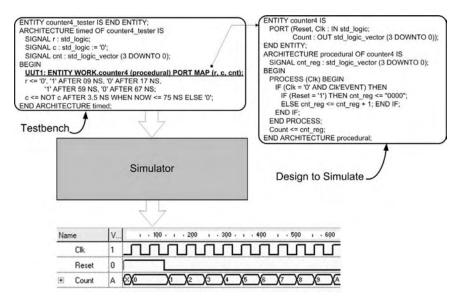

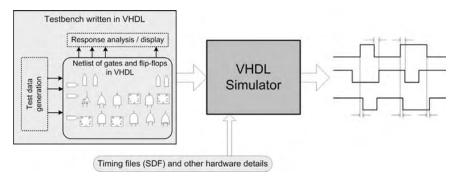

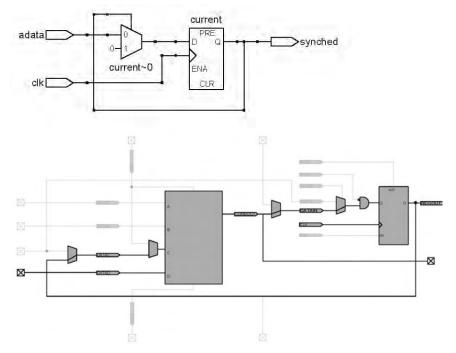

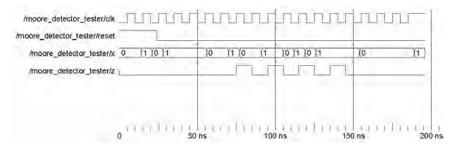

Figure 1.5 VHDL Simulation with a Testbench

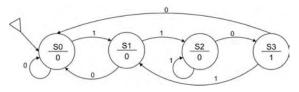

For simulating with a VHDL testbench, the testbench instantiates the design under test, and as part of the code of the testbench it applies test data to the instantiated circuit. Figure 1.5 shows VHDL code of a counter circuit, its testbench, and its simulation results in form of a waveform. As shown here, simulation validates the functionality of the counter circuit being tested. With every clock pulse the counter is incremented by 1. Note in the timing diagram it is shown that the counter output changes with the rising edge of the clock and no gate delays and propagation delays are shown here. Simulation results show a correct functionality of the counter regardless of the clock frequency.

Obviously, an actual hardware component behaves differently. Based on the timing and delays of the parts used, there will be a nonzero delay between the active edge of the clock and the counter output. Furthermore, if the clock frequency applied to an actual part is too fast for propagation of values within the gates and transistors of a design, the output of the design becomes unpredictable.

The simulation shown here is not provided with the details of the timing of the hardware being simulated. Therefore, potential timing

problems of the hardware that are due to gate delays cannot be detected. This is typical of a pre-synthesis or high-level behavioral simulation. What is being verified in Figure 1.5 is that our counter counts binary numbers. How fast the circuit works and what clock frequency it requires can only be verified after the design is synthesized.

**1.3.3.2** Assertion Verification. Instead of having to inspect simulation results manually or by developing sophisticated testbenches, assertion monitors can be used to continuously check for design properties while the design is being simulated. Assertion monitors are put in the design being simulated by the designer. The designer decides that if the design functions correctly, certain conditions have to be met. These conditions are regarded as design properties, and assertion monitors are developed by designer to assert that these properties are not violated. An assertion monitor fires if a design property put in by the designer is violated. This alerts the designer that the design is not functioning according to the designer's expectation. OVL (open verification library) provides a set of assertion monitors for monitoring common design properties. Designers can use their own assertions and use them in conjunction with their testbenches.

**1.3.3.3 Formal Verification.** Formal verification is the process of checking a design against certain properties. When a design is completed, the designer develops a set of properties reflecting correct behavior of his or her design. Without running simulation, and without requiring any simulation data, a formal verification tool examines the design to make sure that the described properties hold under all conditions. If a situation is found that the property will not hold, the property is said to have been violated. Input conditions that make a property to fail are regarded as the property's counter examples. Property coverage indicates how much of the complete design is exercised by the property.

#### 1.3.4 Compilation and Synthesis

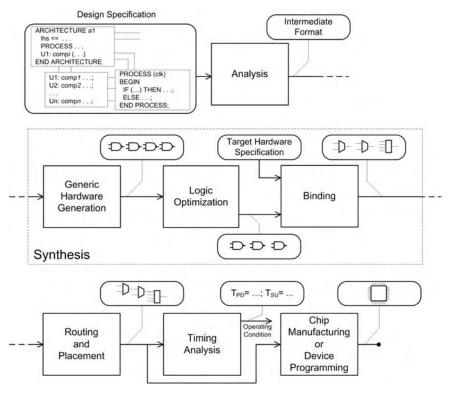

Synthesis is the process of automatic hardware generation from a design description that has an unambiguous hardware correspondence. A VHDL description for synthesis cannot include signal and gate level timing specifications, file handling, and other language constructs that do not translate to sequential or combinational logic equations. Furthermore, VHDL descriptions for synthesis must follow certain styles of coding for combinational and sequential circuits. These styles and their corresponding VHDL constructs are defined under VHDL for RTL synthesis. In the design process, after a design is successfully entered and its pre-synthesis simulation results have been verified by the designer, it must be compiled to make it one step closer to an actual hardware on silicon. This design phase requires specification of the hardware that the design is to be realized in. For example, we have to specify a specific ASIC, or an FPGA part as our "target hardware". When the target hardware is specified, technology files of that hardware (ASIC, FPGA, or Custom IC) with detailed timing and functional specification become available to the compilation process. The compilation process, translates various parts of the design to an intermediate format (analysis phase), links all parts together, generates the corresponding logic (synthesis phase), places and routes components of the target hardware and generates timing details.

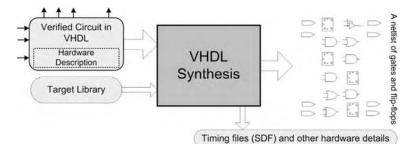

Figure 1.6 Compilation and Synthesis Process

Figure 1.6 shows the compilation process and a graphical representation for each of the compilation phase outputs. As shown, the input of this phase is a hardware description that consists of various levels of VHDL, and its output is a detailed hardware for programming an FPLD (Field Programmable Logic Devices) or manufacturing an ASIC.

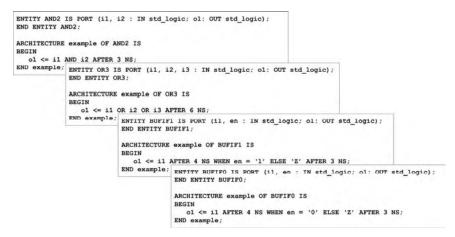

**1.3.4.1 Analysis.** A complete design that is described in VHDL may consist of behavioral VHDL, bus and interconnection specifications, and wiring of other VHDL components. Before the complete design is turned into hardware, the design must be analyzed and a uniform format must be generated for all parts of the design. This phase also checks the syntax and semantics of the input VHDL code.

**1.3.4.2 Generic Hardware Generation.** After obtaining a uniform presentation for all components of a design, the synthesis pass begins its operation by turning the design into a generic hardware format, such as a set of Boolean expressions or a netlist of basic gates.

**1.3.4.3 Logic Optimization.** The next phase of synthesis, after a design has been converted to a set of Boolean expressions, is the logic optimization phase. This phase is responsible for reducing expressions with constant input, removing redundant logic expressions, two level minimization, and multi-level minimization that includes logic sharing.

This is a very computationally intensive process, and some tools allow users to decide on the level of optimization. Output of this phase is in form of Boolean expressions, tabular logic representations, or primitive gate netlists.

**1.3.4.4 Binding.** After logic optimization, the synthesis process uses information from target hardware to decide exactly what logic elements and cells are needed for the realization of the circuit that is being designed. This process is called binding and its output is specific to the FPLD, ASIC, or Custom IC being used.

**1.3.4.5 Routing and Placement.** The routing and placement phase decides on the placement of cells of the target hardware. Wiring inputs and outputs of these cells through wiring channels and switching areas of the target hardware are determined by the routing and placement phase. The output of this phase is specific to the hardware being used and can be used for programming an FPLD or manufacturing an ASIC.

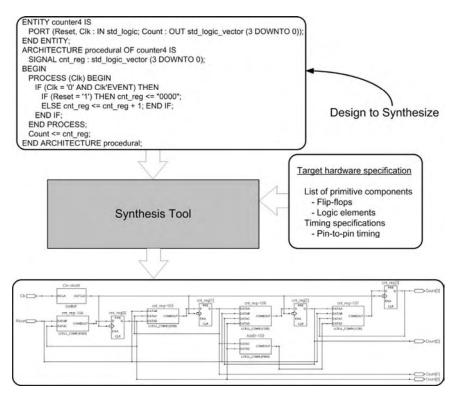

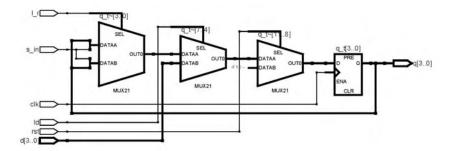

An example of a synthesis run is shown in Figure 1.7. In this figure, the counter circuit used in the simulation run of Figure 1.5 is being synthesized. In addition to the VHDL description of the design, the synthesis tool shown requires specification of the target hardware to synthesize to. The output of the synthesis tool is a list of gates and flip-flops available in the target hardware, and their interconnections. A graphical representation of this output that is automatically generated by the synthesis tool of Altera's Quartus II is shown in Figure 1.7. What is shown here is referred to as the technology map view that shows FPGA cells that are utilized for the implementation of the complete circuit.

Figure 1.7 An Example Synthesis Run

#### 1.3.5 Timing Analysis

As shown in Figure 1.3, as part of the compilation process, or in some tools after the compilation process, there is a timing analysis phase. This phase generates worst-case delays, clocking speed, delays from one gate to another, as well as required setup and hold times. Results of timing analysis appear in tables and / or graphs. Designers use this information to decide on their clocking speed and, in general, speed of their circuits.

#### 1.3.6 Post-Synthesis Simulation

After synthesis is done, the synthesis tool generates a complete netlist of target hardware components and their timings. The details of gates used for the implementation of the design are described in this netlist. The netlist also includes wiring delays and load effects on gates used in the post-synthesis design. The netlist output is made available in various netlist formats including VHDL. Such a description can be simulated and its simulation is referred to post-synthesis simulation. Timing issues, determination of a proper clock frequency and race and hazard considerations can only be checked by a postsynthesis simulation run after a design is synthesized. As shown in Figure 1.3 the same testbench testing the original VHDL design before synthesis can be used for post-synthesis simulation.

Due to delays of wires and gates, it is possible that the behavior of a design as intended by the designer and its behavior after postsynthesis simulation are different. In this case, the designer must modify his or her design and try to avoid close timings and race situations.

#### 1.3.7 Hardware Generation

The last stage in an automated VHDL based design is hardware generation. This stage generates a netlist for ASIC manufacturing, a program for programming FPLDs, or layout of custom IC cells.

#### 1.4 VHDL

The previous section showed steps involved in taking an RT level design from a VHDL description to hardware implementation. This design process is only possible because VHDL is a language that can be understood by system designers, RT level designers, test engineers, simulators, synthesis tools, and machines. Because of this important role in design, VHDL has become an IEEE standard. The standard is used by users as well as tool developers.

#### 1.4.1 VHDL Initiation

In the search for a standard design and documentation tool for the VHSIC (Very High Speed Integrated Circuits) program, the United States Department of Defense (DoD) in the summer of 1981 sponsored a workshop on hardware description languages at Woods Hole, Massachusetts. This workshop was arranged by the Institute for Defense Analysis (IDA) to study various hardware description methods, the need for a standard language, and the features that might be required by such a standard. Because the VHSIC program was under the restrictions of the United States International Traffic and Arms Regulations (ITAR), the VHDL component of this program was also initially subject to such restrictions.

In 1983, DoD established requirements for a standard VHSIC Hardware Description Language (VHDL), based on the recommendations of the "Woods Hole" workshop. A contract for the development of the VHDL language, its environment, and its software was awarded to IBM, Texas Instruments, and Intermetrics corporations. Work on VHDL started in the Summer of 1983. At that time language specifications were no longer under ITAR restrictions, but these restrictions still applied to government developed software.

VHDL 2.0 was released only 6 months after the project began. This version, however, allowed only concurrent statements, and lacked the capability to describe hardware in a sequential softwarelike fashion, a shortcoming that would seriously jeopardize the applicability of the language for high level behavioral descriptions. The language was significantly improved, as this and other shortcomings were corrected when VHDL 6.0 was released in December of 1984. Development of VHDL-based tools also began in 1984.

In 1985, ITAR restrictions were lifted from VHDL and its related software, and the VHDL 7.2 Language Reference Manual (LRM) copyright was transferred to IEEE for further development and standardization. This led to the development of the IEEE 1076/A VHDL Language Reference Manual (LRM), which was released in May of 1987. Later that year version B of the LRM was developed and approved by REVCOM (a committee of the IEEE Standards Board). VHDL 1076-1987 formally became the IEEE standard hardware description language in December of 1987.

Efforts for defining a new version of VHDL started in 1990 by a team of volunteers working under the IEEE DASC (Design Automation Standards Committee). In October of 1992 a new VHDL referred to as VHDL'93 was completed and was released for review. After minor modifications, this new version was approved by the VHDL balloting group members and became the new VHDL language standard. The present VHDL standard is formally referred to as VHDL 1076-1993. Standardization work for this version did not complete until the middle of 1994.

# 1.4.2 Existing Languages

Early in the VHSIC program in 1981 it was found that none of the existing hardware description languages could be used as a standard tool for the design, manufacturing, and documentation of digital circuits ranging from integrated circuits to complete systems. Part of the study for the development of the requirements of a VHSIC language, however, concentrated on the capabilities, shortcomings, and other characteristics of eight hardware description languages that were available at that time. These languages were AHPL, CDL, CONLAN, IDL, ISPS, TEGAS, TI-HDL, and ZEUS. We briefly describe the important features of these languages in order to provide a framework for understanding the VHDL requirements that are discussed in the next section.

**1.4.2.1 AHPL.** AHPL (a hardware programming language) is an HDL for describing hardware at the dataflow level of abstraction. This language uses an implicit clock for synchronizing assignments of data to registers and flip-flops, but does not provide support for describing asynchronous circuits. The language descriptions consist of interacting concurrent modules, and hierarchy of modules is not supported. Data types in AHPL are fixed and restricted to bits, vectors of bits, and arrays of bits. Procedures or functions are only allowed in the context of combinational logic units. Delay and constraint specifications are not allowed in AHPL and assignment of values to buses and registers all occur at the same time without delay, since they are synchronized with an implicit clock.

**1.4.2.2 CDL.** CDL (computer design language) is a hardware description language developed in an academic environment mainly for instruction in digital systems. This language is strictly a dataflow language, and does not support design hierarchy. In CDL, microstatements are used for transfer of data into registers. Conditional micro-statements use if-then-else constructs and can be nested.

**1.4.2.3 CONLAN.** The CONLAN (CONsensus LANguage) project began as an attempt to establish a standard hardware description language. This platform consists of a family of languages for describing hardware at various levels of abstraction. Base CONLAN (bcl ), for example, is the base language for all member languages. All operations in CONLAN are executed concurrently. CONLAN allows hierarchical description of hardware but has limited external use.

**1.4.2.4 IDL.** IDL (interactive design language) is an internal IBM language with limited outside use. IDL was originally designed for automatic generation of PLA structures, but it was later extended to cover more general circuit descriptions. Hardware in IDL can be described in a hierarchy of structures. This language is primarily a concurrent hardware description language.

**1.4.2.5 ISPS.** ISPS (instruction set processor specification) is a very high level behavioral language and was mainly designed to create an environment for designing software based on a given hardware. Although the language is primarily targeted for CPU-like architectures, other digital systems can easily be described in it. Timing control in ISPS is limited. The "NEXT" construct allows timing control between statements of behavioral descriptions, but it is not possible to specify gate level timing and structural details.

**1.4.2.6 TEGAS.** TEGAS (TEst Generation And Simulation) is a system for test generation and simulation of digital circuits. Although several extended versions of this language have behavioral features, the main language (TEGAS Description Language or TDL) is only structural. Digital hardware can be described hierarchically in this language. Detailed timing specification can be specified in TDL.

**1.4.2.7 TI-HDL.** TI-HDL (Texas Instruments Hardware Description Language) is a multi-level language for the design and description of hardware. It allows hierarchical specification of hardware and supports description of synchronous, asynchronous, and combinatorial logic circuits. Behavioral descriptions in TI-HDL are sequential and software-like, and use if-then-else, case, for, and while constructs for program flow control. This language has fixed data types with no provision for adding user defined types.

**1.4.2.8 ZEUS.** The ZEUS hardware description language is a nonprocedural language that was created at General Electric Corporation. This language supports design hierarchy and allows definition of systems by their functionality or their structural arrangements. Timing in ZEUS is at the clock level and there are no provisions for gate delay specification or detailed timing constraints. Because of this timing arrangement, asynchronous circuits cannot be described in ZEUS. This language provides a close link to physical layout.

# 1.4.3 VHDL Requirements

A DoD document entitled "Department of Defense Requirements for Hardware Description Languages", released in January of 1983, clearly stated the requirements for the VHSIC hardware description language. The present VHDL satisfies the requirements set forth in this detailed document. This section briefly describes the main features of VHDL requirements.

**1.4.3.1 General Features.** The DoD requirement document specifies that the VHSIC hardware description language should be a language

for design and description of hardware. It indicates that VHDL should be usable for design documentation, high-level design, simulation, synthesis, and testing of hardware, as well as a driver for a physical design tool.

It emphasizes that VHDL is for the description of hardware from system to gate, and it clearly specifies that system software is not an issue and that physical design does not need to be addressed. Since in an actual digital system, all small or large elements of the system are active simultaneously and perform their tasks concurrently, the concurrency aspect of VHDL is heavily emphasized. In a hardware description language, concurrency means that transfer statements, descriptions of components, and instantiations of gates or logical units are all executed such that in the end they appear to have been executed simultaneously.

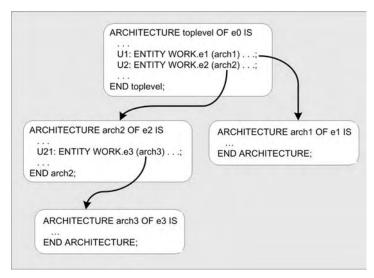

**1.4.3.2 Support for Design Hierarchy.** The DoD requirement document specified the need for hierarchical specification of hardware in VHDL. This feature is essential for a multi-level hardware language. A design consists of an interface description and a separate part for describing its operation. Several descriptions may exist for describing the operation of a design, all corresponding to the same interface description. The operation of a system can be specified based on its functionality, or it can be specified structurally in terms of its smaller sub-components. Structural description of a component can be accomplished at all design levels. At the lowest levels, components are described by their functionality and use no sub-components.

**1.4.3.3 Library Support.** For design management, the need for libraries is specified for VHDL. User defined and system defined primitives and descriptions reside in the library system. The language should provide mechanism for accessing various libraries. A library can contain an interface description of a design. At the same time, several specifications of the operation of this design can simultaneously reside in this library.

Descriptions and models that are correct should be placed in the library after the language compiler has compiled them. In addition, libraries should be accessible to different designers.

**1.4.3.4 Sequential Statement.** Although the strong features of a hardware description language should be its support for concurrent execution of processes and statements, the VHDL language requirements also specified the need for software-like sequential control. When a hardware designer partitions a system into concurrent components or subsections, the designer should then be able to describe

the internal operational details by sequential programming language constructs such as case, if-then-else, and loop statements.

Sequential statements provide an easy method for modeling hardware components based on their functionality. Sequential or procedural capability is only for convenience and the overall structure of the VHDL language remains highly concurrent.

**1.4.3.5 Generic Design.** In addition to inputs and outputs of a hardware component, other conditions may influence the way it operates. These include the environment where the hardware component is used, and the physical characteristics of the hardware component itself. It should not be necessary to generate a new hardware description for every specific condition. Furthermore, many hardware components in various logic families or FPGAs are functionally equivalent, and differ only in their timing and loading characteristics. For example, logic elements in Altera's Cyclone, Cyclone II, and Stratix are very similar in cell structure but have different timing properties.

A good hardware description language should allow the designer to configure the generic description of a component when it is used in a design. Generic descriptions should be configurable for size, physical characteristics, timing, loading, and environmental conditions. The ability to describe generic models of hardware was a DoD requirement for the VHDL language.

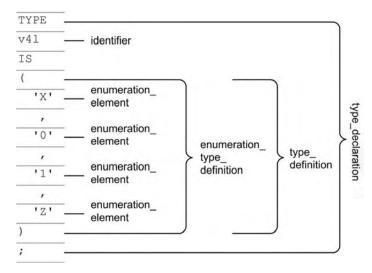

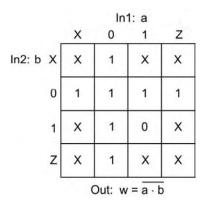

**1.4.3.6 Type Declaration and Usage.** A language for the description of hardware at various levels of abstractions should not be limited to Bit or Boolean types. VHDL requirements specified that the language ought to allow integer, floating point, and enumerate types, as well as user defined types. Types defined by the system or by the user should be placed in the library of the language environment and their use should be transparent to the user.

The language should provide the capability to redefine language operators for types that are defined by the user. For example, the language provides Boolean operators such as AND, OR, and NOT for the predefined logic values. A user needing a multi-level logic should be able to redefine these operators for the newly defined multi-level logic type.

In addition, a hardware description language should allow array type declarations and composite type definitions, such as structures or records in programming languages. The DoD document also specified a strongly typed language and strong type checking.

**1.4.3.7 Use of Subprograms.** The ability to define and use functions and procedures was another VHDL requirement. Subprograms can be used for explicit type conversions, logic unit definitions, operator re-

definitions, new operation definitions, and other applications commonly used in programming languages.

**1.4.3.8 Timing Control.** The ability to specify timing at all levels is another requirement for the VHDL language. VHDL should allow the designer to schedule values to signals and delay the actual assignment of values until a later time. For handshaking and gate or line delay modeling in the sequential descriptions, it should be possible to wait for the occurrence of an event or for a specific time duration.

The language should be general and should allow any number of explicitly defined clock signals. The clocking scheme should be completely up to the user, since the language does not have an implicit clocking scheme or signal.

Constructs for edge detection, delay specification, setup and hold time specification, pulse width checking, and setting various time constraints should be provided.

**1.4.3.9 Structural Specification.** The DoD requirements for a standard hardware description language specified that the language should have constructs for specifying structural decomposition of hardware at all levels. It also should be possible to describe a generic one-bit design and use it when describing multi-bit regular structures in one or more dimensions. This requires constructs for iteration in the description of structures.

# 1.4.4 The VHDL Language

In its present form, VHDL satisfies all requirements of the 1983 DoD requirements document. The experience, researchers, software developers, and other users with VHDL since it became the IEEE standard in 1987 indicates this language is sufficiently rich for designing and describing today's digital systems.

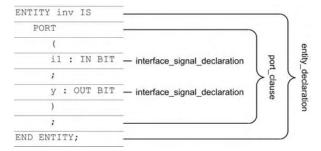

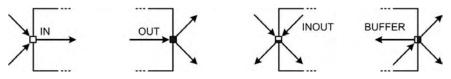

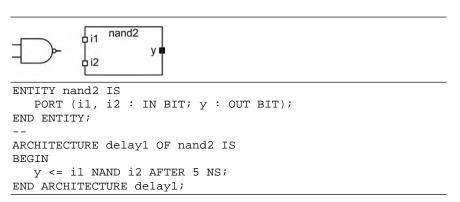

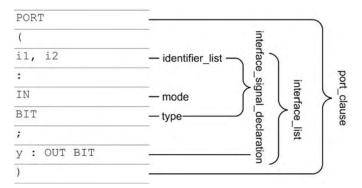

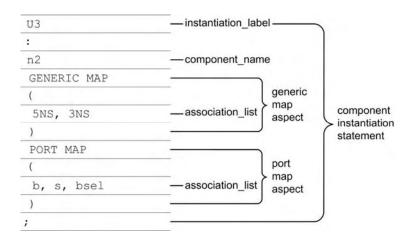

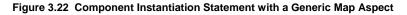

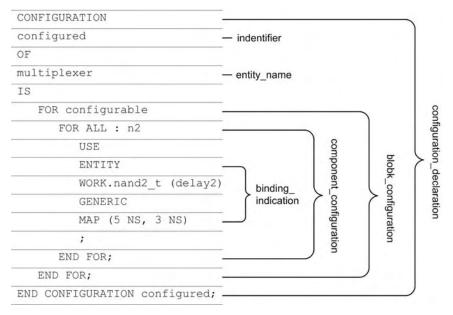

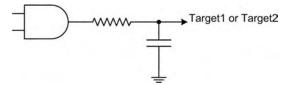

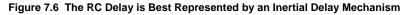

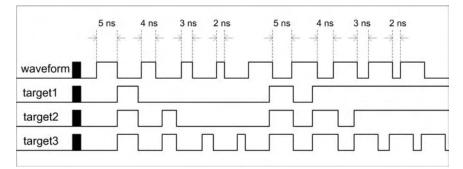

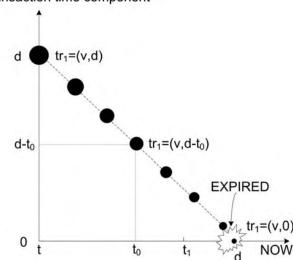

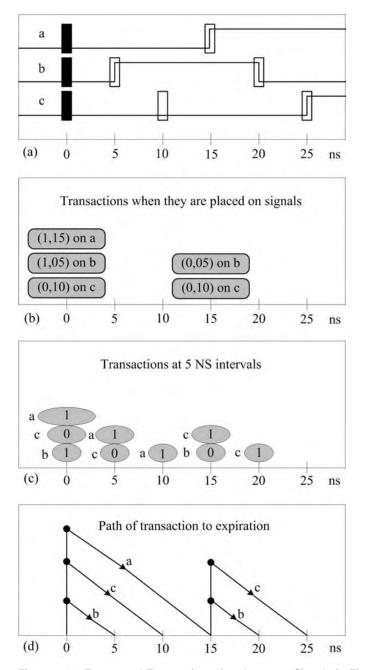

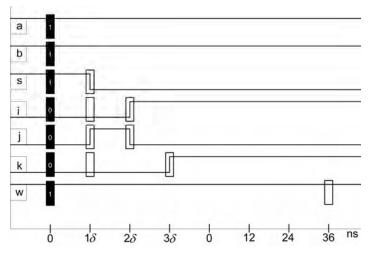

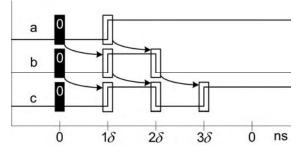

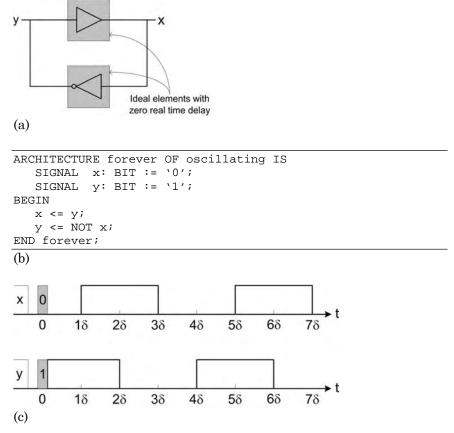

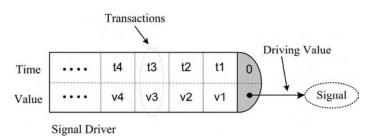

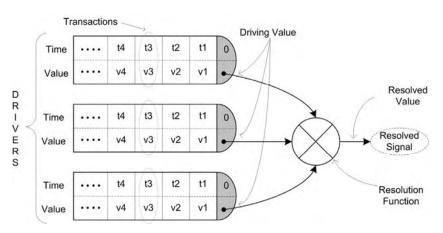

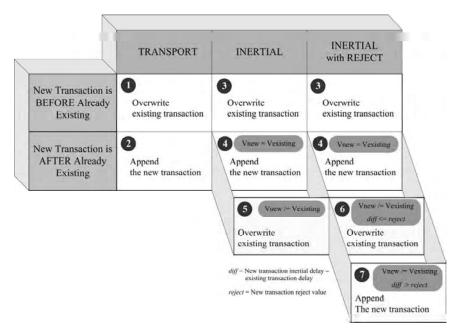

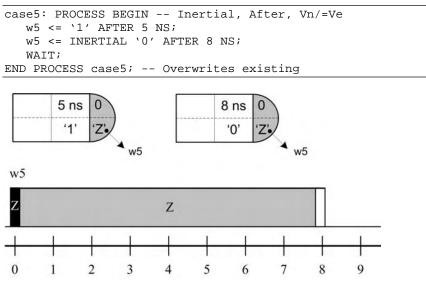

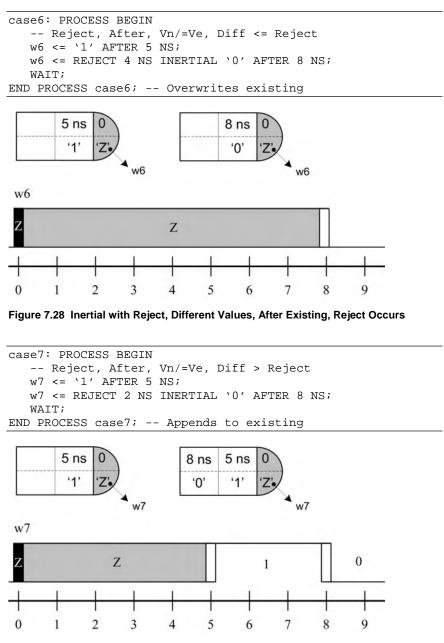

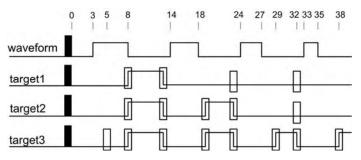

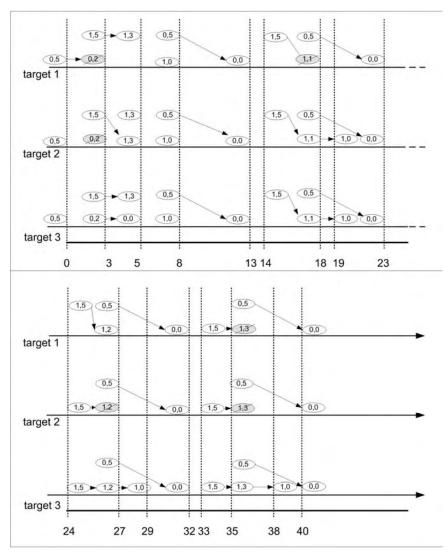

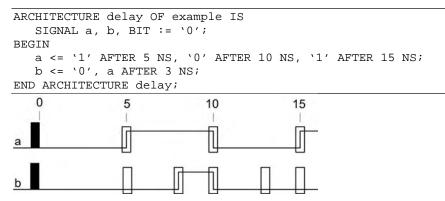

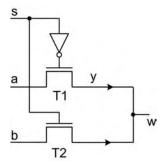

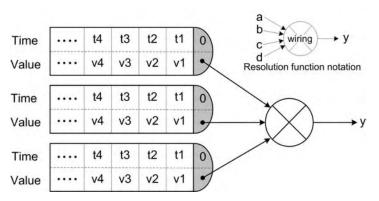

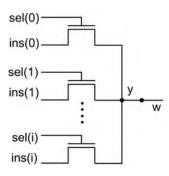

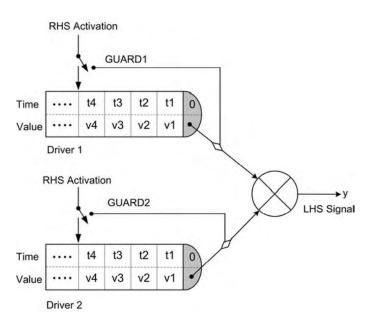

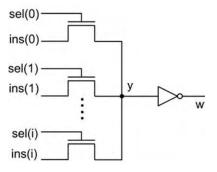

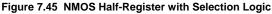

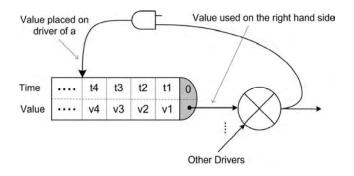

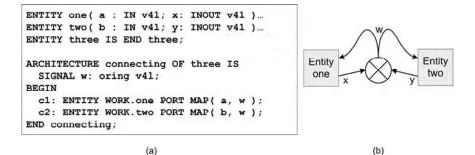

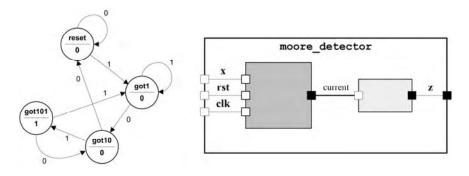

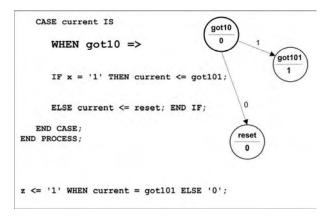

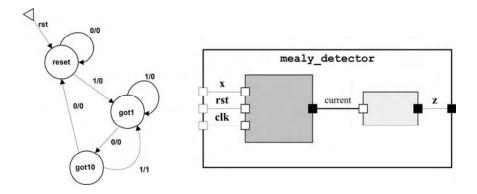

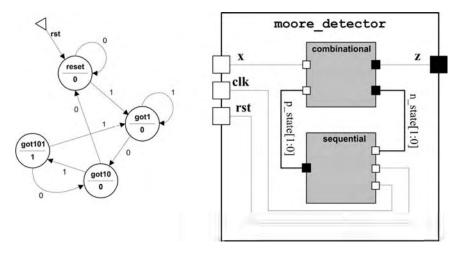

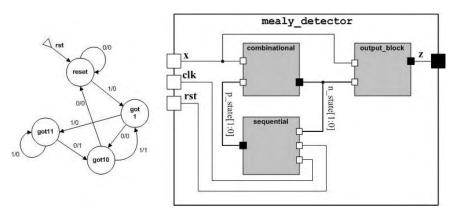

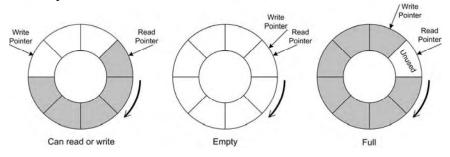

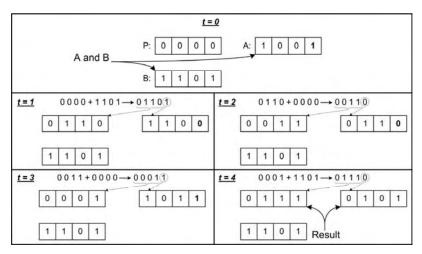

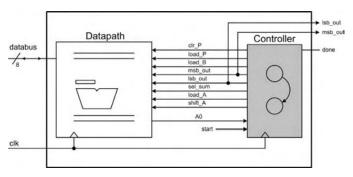

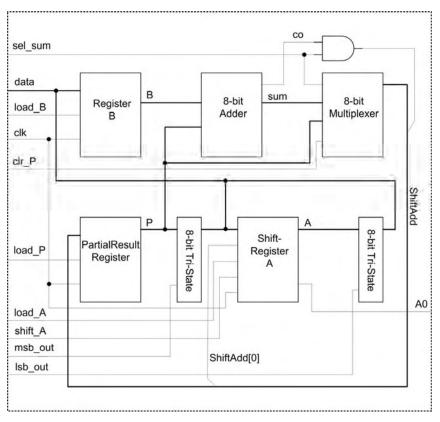

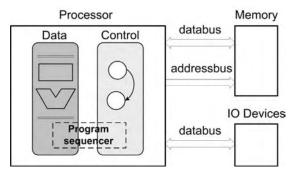

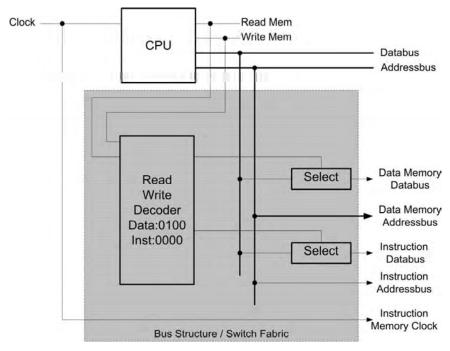

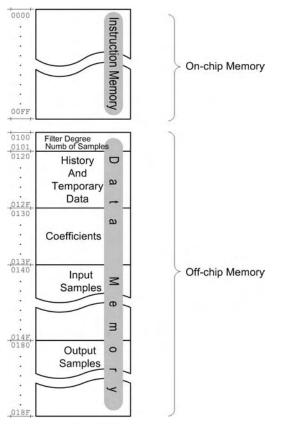

As originally required, VHDL is a hardware description language with strong emphasis on concurrency. The language supports hierarchical description of hardware from system to gate or even switch level. VHDL has strong support at all levels for timing specification and violation detection. As expected, VHDL provides constructs for generic design specification and configuration.